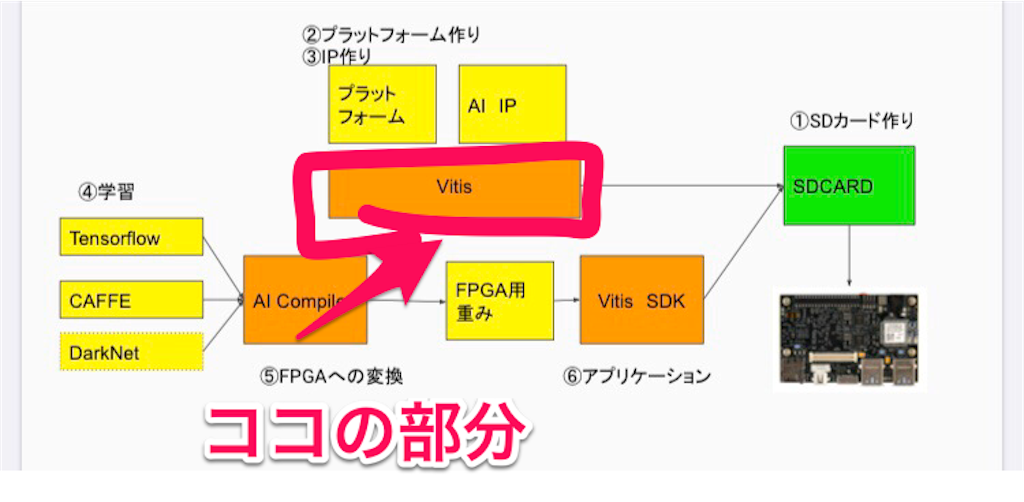

前回の続編のpart3。Vivadoでultra96のデザインブロックとかXSAファイルを作成した後、PetaLinuxでVitisプラットフォーム(vitis IDE)立ち上げまでやっていく。

part3の作業で完了するのは「vitis IDE」構築のvitisの部分。

メインでにやること

・vitis IDEの立ち上げ

手順はほぼ本家のサイト「Ultra96用Vitisプラットフォームの作り方(BASE編)」通り作業していく。

ただVivadoで作成するXSAファイルは本家サイト通りやってもエラーが出て作成できなかったので、Xilinxのgithubのファイルで代用した。

Alternative XSA file at GitHub

目次

1.Vivadoでのハードウェア設計

2.PetalinuxでLinuxシステムの設計

3.Vitis IDEを立ち上げてみる

1.Vivadoでのハードウェア設計

Vivadoでultra96v2で動作させるハードウェアを設計。

今回は参考サイトのだと何故かうまくいかないので、Xilinxのgithubから代用のXSAファイルを使う。

一応、ultra96で使うまでのハードウェア設計の手順だけまとめていく。ここはほぼ本家と同じ

1.新規プロジェクトと新規ブロックデザインの作成

・Project location: /home/[host-name]/ultra96base

・Project type:RTL Project

(「Do not specify sources at this time」のブロックにチェックを入れた)

***Project再開方法

Open ProjectからProjectを作ったフォルダの[プロジェクト名.xpr]を選択し、再開。

右の[Flow Navigator]でIP INTEGRATOR => Create Block Design => ブロックデザイン名を決める。

デフォルでいいのでOKで作成。

2.Blockの配置・配線

デザインを作成すると、キャンパスが出てくるのでブロック追加・配線をする。ここは本家サイトと同じなので

・簡単な流れ

・エラーになる箇所のポイント

をまとめた。

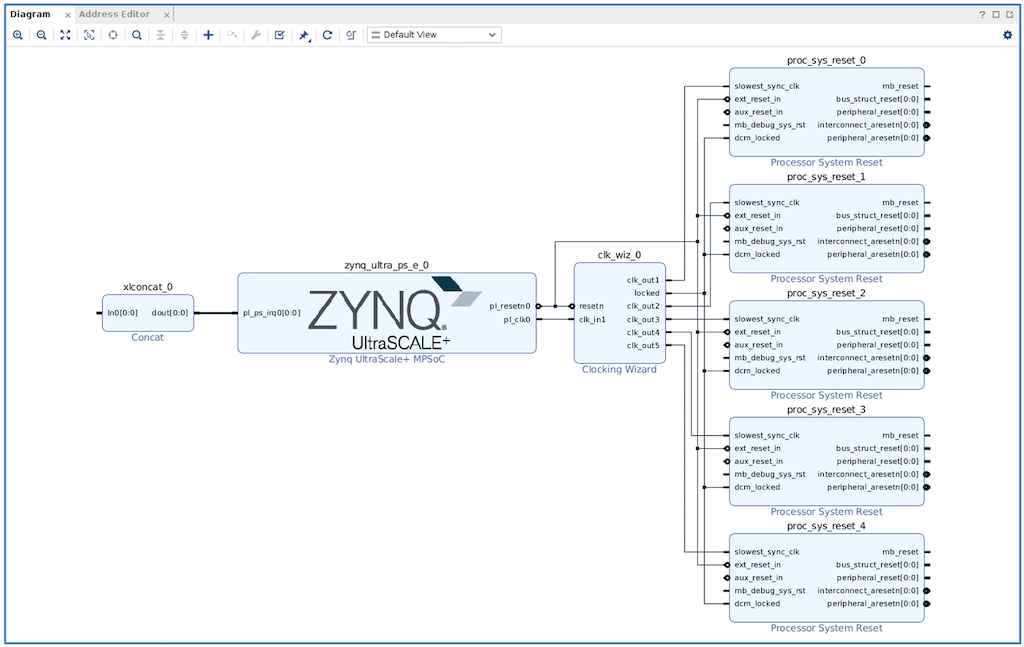

[Search]からzynqを入力して[Zynq UltraScale+ MPSoC]を選択・配置して、[Run Block Automation]をクリックし、デフォルト値のままOK。

下図のように配線

配線実行例

完全に慣れなので一つずつ確実に配線してく。

3.プラットフォーム(PFM)インターフェースとプロパティの定義

***ここ大事

・clk_outのidをclk_out1から順にidを0, 1, 2にする(clk_out2, 3はidを1, 2に変更)

18- Select the enabled clk_out1 and in the Options window change the id to 0 and select the is_default. Note, to change the id filed you must press the Enter key on your keyboard. Change ids of clk_out2, clk_out3, and clk_out4 to 1, 2, and 3, respectively.

引用元:How to create Ultra96v2 Linux-based Platform in Xilinx Vitis 2019.2

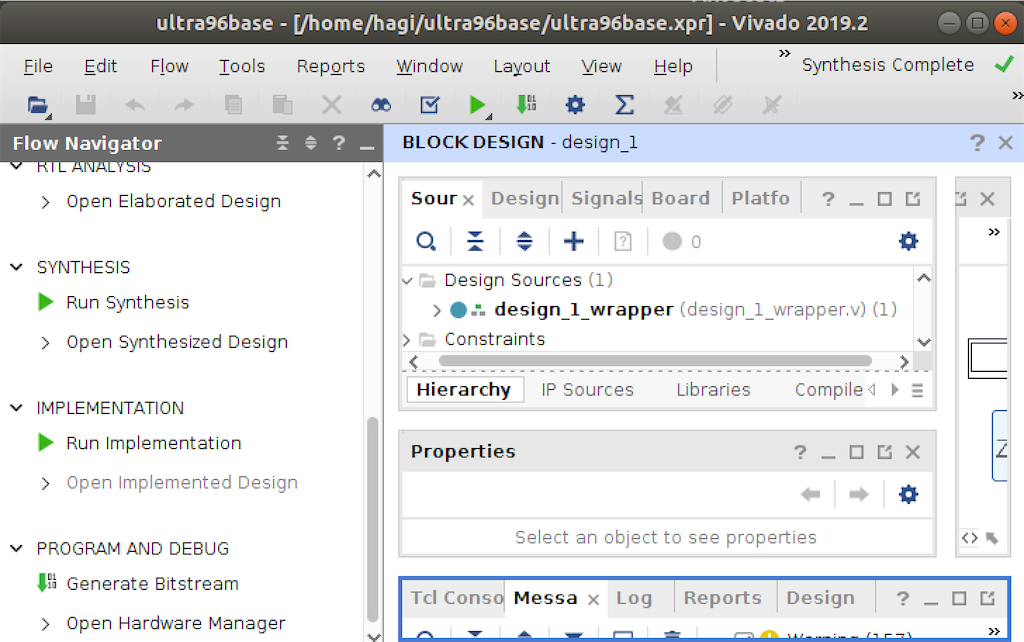

4.XRT用の設定から[BitStream]まで

set_property platform.design_intent.embedded true [current_project] set_property platform.design_intent.server_managed false [current_project] set_property platform.design_intent.external_host false [current_project] set_property platform.design_intent.datacenter false [current_project] set_property platform.default_output_type "sd_card" [current_project]

=>オレンジから青のファイル(ultra96base_wrapper(ultra96base_wrapper.v))に変わる

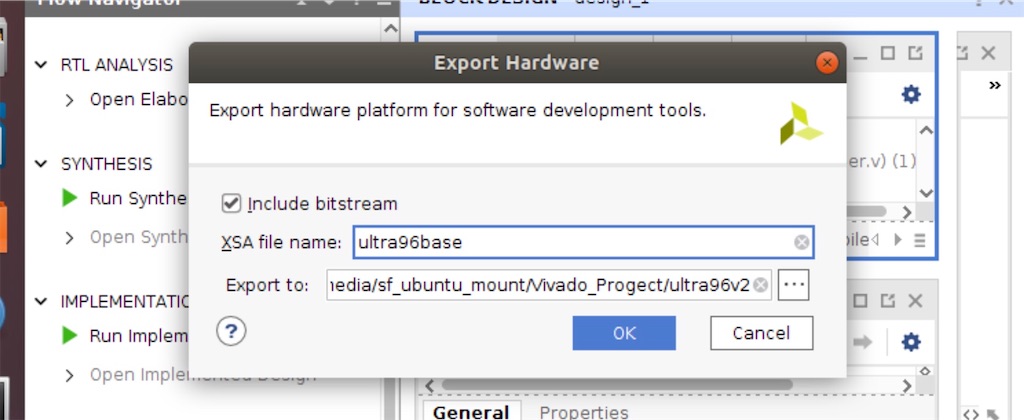

5.XSAファイルの作成

Vivadoのメニューから [File] → [Export]→[Export Hardware]

をクリック。

[include bitstream]にチェックをいれて、デザインの名前を[ultra96base](プロジェクト名と同じ)に変更

XSAファイルの名前をプロジェクト名と同じ「ultra96base.xsa」にするのは下の理由から。

・アクセレーション・プラットフォームとVitisに認識させるにはハードとソフトの名前の一致が重要な要件だから

ちゃんとできてるなら、エラーが出ないで成功

$ validate_hw_platform <Write Path>/ultra96base.xsa >>> INFO: [Vivado 12-6074] Validating Hardware Platform: ‘/home/[host-name]/ultra96base/ultra96base.xsa’ 〜略〜 INFO: [Vivado 12-6067] Found file 'ultra96base.bit' of type 'FULL_BIT' in the Hardware Platform. INFO: [Vivado 12-6066] Finished running validate_dsa for file: '/home/[host-name]/ultra96base/ultra96base.xsa'

2.PetalinuxでLinuxシステムの設計

PetaLinuxシステムで、Ultra96の動作に必要なBIFファイルと、Vitis IDEに必要なSDKファイルを作成してく。

メインでやること

・ultra96の動作に必要なBIFファイルの作成

・vitis IDE立ち上げ

1.Petalinux用のプロジェクトの作成

プロジェクトのファルダ内(/home/[host-name]/ultra96base)で実行。

# ディレクトリ構成 $ tree /home/[host-name]/ultra96base └── <略> └──ultra96base.xpr └──ultra96base.xsa # git cloneしてきたものなので権限付与 $ sudo chmod 777 ultra96base.xsa # プロジェクト作成 $ petalinux-create -t project -n petalinux --template zynqMP >>> INFO: Create project: petalinux INFO: New project successfully created in /opt/petalinux/petalinux

2.Vivadoで作成したXSAファイルの取り込み

$ cd petalinux $ petalinux-config ―get-hw-description=/home/[host-name]/ultra96base

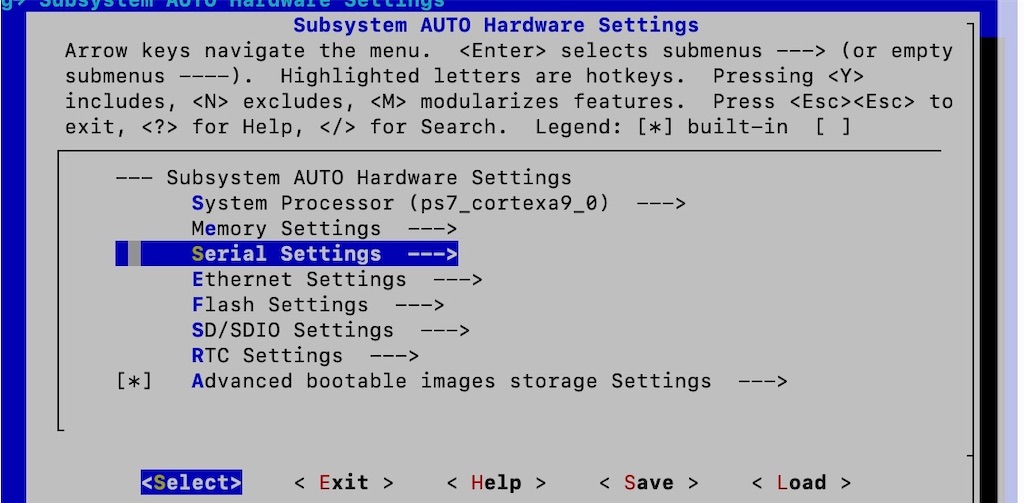

コンソールによるメニュー形式が出てくるので本家の通り操作。

DTG Settngs → MACHINE_NAMEを[avnet-ultra96-rev1]

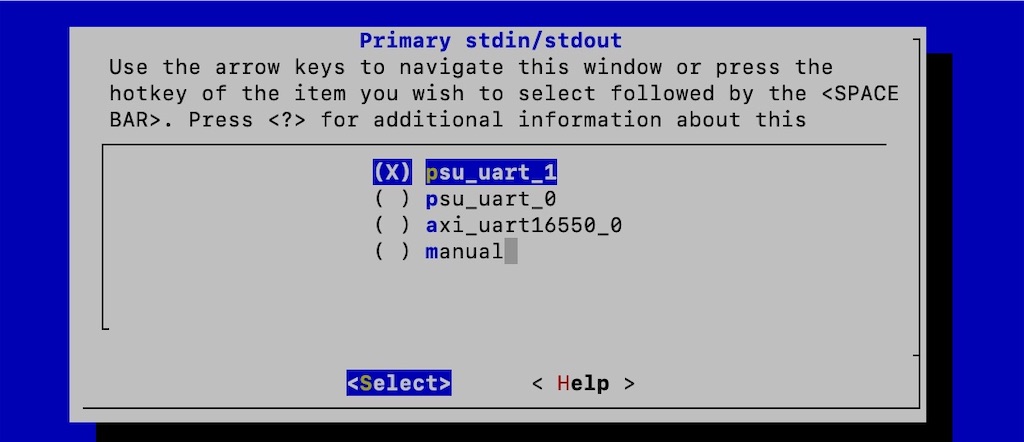

[Exit]で戻り、Subsystem AUTO Hardware Settings → Serial Settings を設定、その後、[psu_uart_1]に設定

次にシステムを増やすために、SDカードの記録方法を指定。

2回[Exit]でトップメニューから、[Image Packageing Configuration] => [Root filesystem type] から[EXT(SD/eMMC/QSPI/STAT/USB)]を[select]で選択。

選択して[Exit]を2回。その後、「保存しますか」を聞いてくるので、Yesをクリック。

完了まで時間がかかるのでコーヒーブレイク。

出力ログ

INFO: Getting hardware description... INFO: Rename ultra96base.xsa to system.xsa [INFO] generating Kconfig for project [INFO] menuconfig project configuration written to /home/[host-name]/ultra96base/petalinux/project-spec/configs/config *** End of the configuration. *** Execute 'make' to start the build or try 'make help'. 〜略〜 [INFO] silentconfig rootfs [INFO] generating petalinux-user-image.bb

# ファルダ状況確認 $ ls >>> build components config.project project-spec

3.ファイルの追加・編集

# XRTを使えるようにするため追記 $ sudo vi /home/[host-name]/ultra96base/petalinux/project-spec/meta-user/conf/user-rootfsconfig

#Note: Mention Each package in individual line #These packages will get added into rootfs menu entry CONFIG_gpio-demo CONFIG_peekpoke CONFIG_xrt CONFIG_xrt-dev CONFIG_zocl CONFIG_opencl-clhpp-dev CONFIG_opencl-headers-dev CONFIG_packagegroup-petalinux-opencv

# Zynqシリーズで、XRTドライバーが使えるようにする $ sudo vi /home/[host-name]/ultra96base/petalinux/project-spec/meta-user/recipes-bsp/device-tree/files/system-user.dtsi

/include/ "system-conf.dtsi"

/ {

};

&amba {

zyxclmm_drm {

compatible = "xlnx,zocl";

status = "okay";

};

};上の設定したファイルを有効可するため下コマンドを実行。

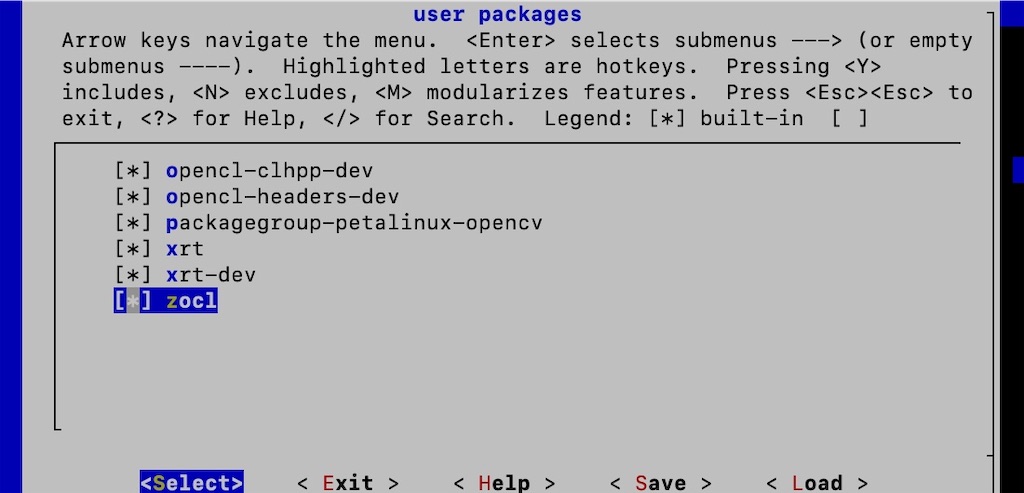

コンソールによるメニュー形式が出てくるので[user packages]を選択。

出ているプログラムでスペースキーをクリックしてすべて有効にする。

2回[Exit]で、セーブして、Yesで保存。

$ cd && cd ultra96base/petalinux $ petalinux-config -c rootfs >>> [INFO] sourcing bitbake [INFO] generating plnxtool conf 〜略〜 [INFO] menuconfig rootfs configuration written to /home/[host-name]/ultra96base/petalinux/project-spec/configs/rootfs_config *** End of the configuration. *** Execute 'make' to start the build or try 'make help'. [INFO] generating petalinux-user-image.bb [INFO] successfully configured rootfs

ここも本家通り操作。

$ petalinux-config -c kernel >>> [INFO] generating Kconfig for project ~略~ NOTE: Source tree extracted to /home/[host-name]/ultra96base/petalinux/components/plnx_workspace/sources/linux-xlnx WARNING: SRC_URI is conditionally overridden in this recipe, thus several devtool-override-* branches have been created, one for each override that makes changes to SRC_URI. It is recommended that you make changes to the devtool branch first, then checkout and rebase each devtool-override-* branch and update any unique patches there (duplicates on those branches will be ignored by devtool finish/update-recipe) NOTE: Recipe linux-xlnx now set up to build from /home/[host-name]/ultra96base/petalinux/components/plnx_workspace/sources/linux-xlnx ~略~ NOTE: Updating config fragment /home/[host-name]/ultra96base/petalinux/components/plnx_workspace/sources/linux-xlnx/oe-local-files/devtool-fragment.cfg [INFO] successfully configured kernel

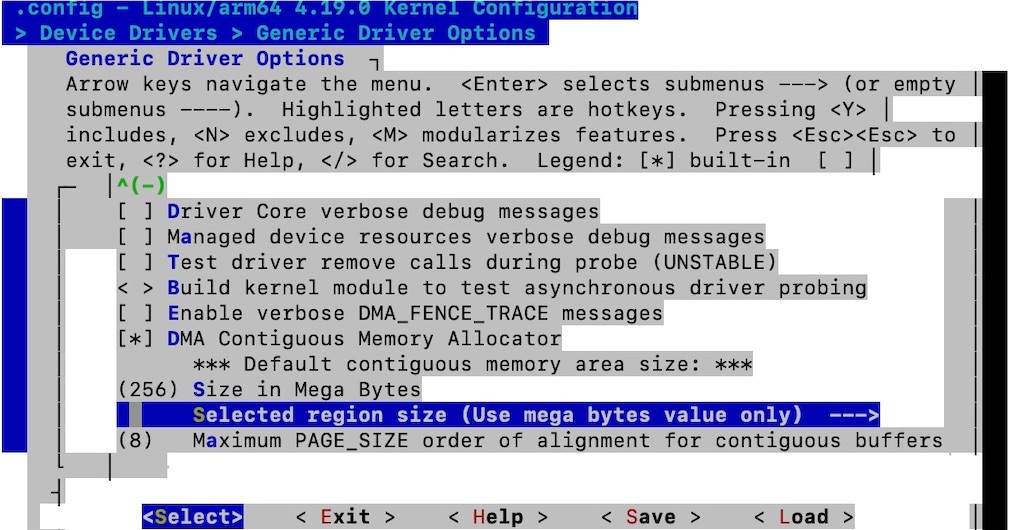

ここでコンソールによるメニュー形式が出てくるので本家の通り操作。

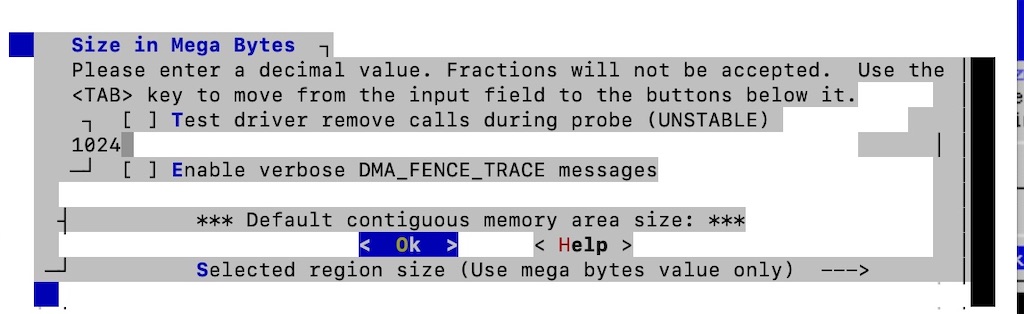

[Device Drivers]→ [Generic Driver Options]→ [DMA Contiguous Memory Allocator] → [Size in Mega Bytes]をクリックして、256を1024に変更。

[Exit]=>[Save]で保存して終わり。

ここまでで、コンフィグレーションの設定は終わり。

5.ビルドしてSDKファイルの作成

2箇所ビルドをします。かなり時間がかかるところなので、気長に。

1回目のbuildが終わった時点で、Petalinux-packgeを使って、BOOT.BINファイルを作成して、SDカードにコピーすれば、Ultra96が動作可能。(今回はしない)

# 1回目のビルド $ petalinux-build >>> [INFO] building project ~略~ NOTE: Resolving any missing task queue dependencies WARNING: /opt/petalinux/components/yocto/source/aarch64/layers/meta-xilinx/meta-xilinx-bsp/recipes-kernel/linux/linux-xlnx_2019.2.bb.do_compile is tainted from a forced run ~略~ NOTE: linux-xlnx: compiling from external source tree /home/[host-name]/ultra96base/petalinux/components/plnx_workspace/sources/linux-xlnx ~略~ INFO: Creating /home/[host-name]/ultra96base/petalinux/images/linux directory NOTE: Failed to copy built images to tftp dir: /tftpboot [INFO] successfully built project

# ファルダ状況確認 $ ls >>> build components config.project images project-spec

# 2回目のビルド $ cd images/linux $ petalinux-build --sdk >>> [INFO] building project ~略~ WARNING: /opt/petalinux/components/yocto/source/aarch64/layers/meta-xilinx/meta-xilinx-bsp/recipes-kernel/linux/linux-xlnx_2019.2.bb.do_compile is tainted from a forced run Initialising tasks: 100% ~略〜 [INFO] Copying SDK Installer... [INFO] successfully built project # sdk.shが出来てるか確認 $ ls ~~~ pxelinux.cfg sdk.sh zynqmp-qemu-multiarch-pmu.dtb rootfs.cpio system.bit zynqmp_fsbl.elf

sdk.shは自己解凍ファイルなので解凍して、Vitis IDEのsysrootにする。

$ cd ../../.. && mkdir pfm $ ./petalinux/images/linux/sdk.sh

出力する場所のパスを聞いてくるので、パス(今回は/home/[host-name]/ultra96base/pfm)を指定。

PetaLinux SDK installer version 2019.2 ====================================== Enter target directory for SDK (default: /opt/petalinux/2019.2): /home/[host-name]/ultra96base/pfm You are about to install the SDK to "/home/[host-name]/ultra96base/pfm". SDK............................................................done Setting it up...done SDK has been successfully set up and is ready to be used. Each time you wish to use the SDK in a new shell session, you need to source the environment setup script e.g. $ . /home/[host-name]/ultra96base/pfm/environment-setup-aarch64-xilinx-linux # 確認 $ ls pfm >>> environment-setup-aarch64-xilinx-linux sysroots site-config-aarch64-xilinx-linux version-aarch64-xilinx-linux

最後にVitis IDE作成時にブートするファイルのコピー

$ mkdir boot && cd petalinux/images/linux $ cp image.ub zynqmp_fsbl.elf pmufw.elf bl31.elf u-boot.elf ../../../boot $ cd ../../..

6.BIFファイルの作成

BIFファイルはSDカードを作るときに必要。作成には下のテキストファイルをboot/linux.bif としてそのまま作成

$ sudo vi boot/linux.bif

/* linux */

the_ROM_image:

{

[fsbl_config] a53_x64

[bootloader] <zynqmp_fsbl.elf>

[pmufw_image] <pmufw.elf>

[destination_device=pl] <bitstream>

[destination_cpu=a53-0, exception_level=el-3, trustzone] <bl31.elf>

[destination_cpu=a53-0, exception_level=el-2] <u-boot.elf>

}3.Vitis IDEを立ち上げてみる

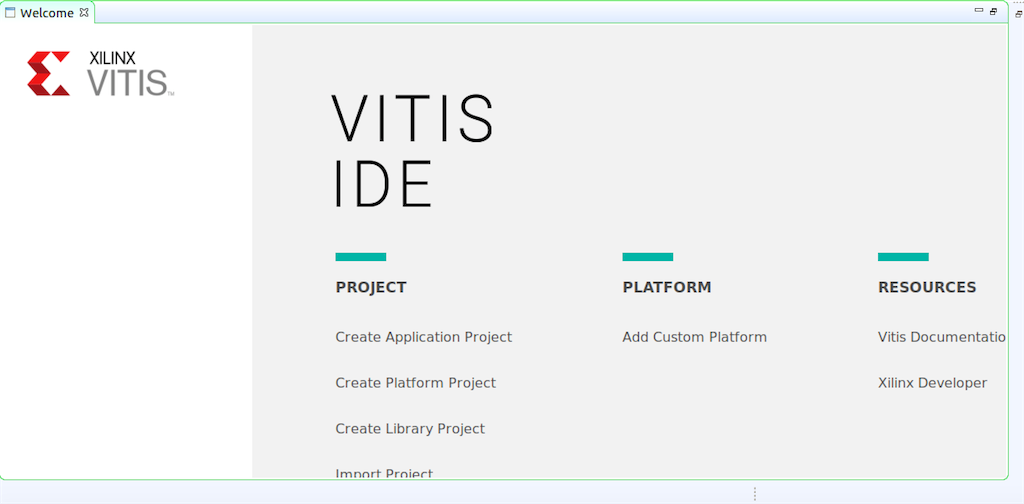

Vitis IDEを起動してみる。

$ cd /home/[host-name]/ultra96base/pfm $ vitis -workspace wksp1

無事立ち上がった。

PCが低スペックすぎるので、Petalinuxのビルドのところでとんでもなく時間かかった。2017年以降のMacなら割と早く終わるはず。

参考サイト

・Ultra96-V2 の Vitis アクセラレーション・プラットフォームの作り方(ハードウェア・コンポーネント編)

・Running Ubuntu on Ultra96v2 Using Petalinux 2019.2, with Networking

・Xlinx-2018.3 SDSoC™ Development Environment Tutorials

・How to create Ultra96v2 Linux-based Platform in Xilinx Vitis 2019.2